Renesas Electronics präsentiert neue, innovative Low-Power SRAM-Produkte für höhere Zuverlässigkeit im Systemeinsatz

Von Renesas Electronics Europe

Erweiterung des Produktangebots innovativer Low-Power SRAM-Produktserien in 110-nm-Prozesstechnologie mit hoher Unempfindlichkeit gegenüber Soft Errors

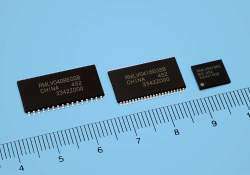

Düsseldorf, 24.09.2013 - Renesas Electronics präsentiert zwölf neue Produktversionen seiner Serien RMLV0416E, RMLV0414E und RMLV0408E. Diese Advanced LP SRAM (Advanced Low-Power SRAM) Produktfamilien zählen zu den leistungsfähigsten SRAM-Bausteinen (Static Random Access Memory) des Anbieters. Die neuen Speicherbausteine bieten einen Speicherumfang von 4 Mb und nutzen Prozesstechnologie mit 110 Nanometer (nm) Strukturbreite.

Die neuen SRAMs gehören zu einer neuen Reihe von innovativen LPSRAMs und entsprechen mit ihrer hohen Zuverlässigkeit bestehenden Renesas SRAM-Produkten in 150 nm Prozesstechnologie. Dies gilt insbesondere für die Vermeidung von Soft Errors (siehe Anmerkung 1) und Latch-up-Effekten (siehe Anmerkung 2). Mit einem Standby-Strom von maximal 2 Microampere (µA) bei 25°C ermöglichen sie einen Low-Power Betrieb und eignen sich damit für die Datenspeicherung in batteriebetriebenen Geräten.

Die Low-Power SRAMs von Renesas finden einen breiten Einsatz in vielen unterschiedlichen Einsatzgebieten, wie etwa in Industrieelektronik, Büro- und Kommunikationstechnik, Automobil- und Unterhaltungselektronik. Im Jahr 2012 war Renesas die Nummer eins weltweit bei den Marktanteilen für solche Produkte (siehe Anmerkung 3). Die jüngste Entwicklung bei Herstellersystemen zielt auf höhere Leistung und breiteren Funktionsumfang, weshalb SRAMs heute eine wichtige Rolle bei der Verbesserung der Gesamt-Systemzuverlässigkeit spielen. Vor allem SRAMs zur Speicherung wichtiger Informationen wie etwa von Systemprogrammen oder Abrechnungsdaten müssen ein hohes Maß an Zuverlässigkeit bieten. Besonders wichtig sind dabei Maßnahmen zur Verringerung von Soft Errors, die durch Alpha- oder kosmische Neutronenstrahlung verursacht werden.

Spezielle Strukturen im Inneren der Advanced LP SRAM Bausteine von Renesas gewährleisten eine außerordentlich hohe Unempfindlichkeit gegenüber Soft Errors: Jeder Speicherknoten (siehe Anmerkung 4) innerhalb der Speicherzellen besitzt einen zusätzlichen physikalischen Kondensator (siehe Anmerkung 5). Eine beliebte Methode zum Schutz vor Soft Errors besteht darin, dass man eine interne ECC-Schaltung (Error Correction Code) in den SRAM oder in den Systemen des Herstellers integriert, um Fehler nach ihrem Auftreten zu korrigieren. Dieser Ansatz stößt jedoch an seine Grenzen, wenn der ECC Fehler an mehreren Bits korrigieren muss. Im Unterschied dazu nutzen Advanced LP SRAMs strukturelle Maßnahmen, die schon das Auftreten von Soft Errors verhindern. Die Ergebnisse aus der Evaluation von System Soft Errors in 150 nm Advanced LP SRAMs aus aktueller Großserienfertigung belegen, dass diese Produkte praktisch keine Soft Errors mehr aufweisen.

Zusätzlich sind die (P-Kanal) Last-Transistoren der SRAM-Zellen aus Polysilizium-TFTs (siehe Anmerkung 6) realisiert, die über den N-Kanal MOS-Transistoren auf dem Silizium-Substrat angeordnet sind. Es werden also nur die unten liegenden N-Kanal Transistoren auf dem Silizium-Substrat erzeugt. Dies gewährleistet, dass sich keine parasitären Thyristoren innerhalb des Speicherbereichs bilden können, was Latch-ups theoretisch unmöglich macht.

Dank dieser Funktionsmerkmale können Advanced LP SRAMs ein wesentlich höheres Niveau an Zuverlässigkeit erreichen als reine CMOS-Produkte (siehe Anmerkung 7) mit herkömmlicher Speicherzellen-Struktur. Advanced LP SRAMs ermöglichen eine noch bessere Leistung und Zuverlässigkeit in Anwendungen, bei denen ein hohes Maß an Zuverlässigkeit entscheidend ist, so zum Beispiel in Fabrikautomationssystemen, Messgeräten, Geräten für den Einsatz in intelligenten Stromnetzen sowie in Transportsystemen.

Um die Zellengröße noch weiter zu verringern, kombinieren Advanced LP SRAMs außerdem eine SRAM-Polysilizium-TFT-Stacking-Technologie mit einer Stacked-Capacitor-Technologie. Damit ist die Zellengröße eines Advanced LP SRAMs in 110-nm-Technologie vergleichbar mit der eines in 65-nm-Technologie gefertigten reinen CMOS-SRAMs.

Renesas plant, die Produktpalette seiner 110-nm-SRAMs in Zukunft um weitere 110-nm-Produkte mit 8 Mb und 64 Mb zu ergänzen.

Die wichtigsten Spezifikationen der neuen SRAM-Bausteine sind auf einem separaten Datenblatt abrufbar.

Anmerkung 1) Soft Error:

Der Soft Error ist ein Phänomen, bei dem eine elektrische Ladung entsteht, wenn eine externe Alpha- oder Neutronenstrahlung auf das Silizium-Substrat trifft, wobei die im Speicher abgelegten Daten verloren gehen. Im Gegensatz zu einem Hard Error wie etwa dem physikalischen Ausfall eines Halbleiterelements, die nachvollziehbar sind, sind Soft Errors nicht reproduzierbar und lassen sich nur durch ein erneutes Schreiben der Daten korrigieren. Prinzipiell steigt die Häufigkeit von Soft Errors, je feiner die geometrischen Strukturen des Fertigungsprozesses werden.

Anmerkung 2) Latch-up:

Das Latch-up-Phänomen ist ein niederohmiger Zustand, der zu einem Kurzschluss führen kann. Durch immer kleinere Prozesse wird die Distanz zwischen den P- und N-Channel Transistoren auf der Siliziumoberfläche immer geringer, was zu Überspannung, elektrostatischer Ladung oder Alpha-/Neutronstrahlung auf der Siliziumoberfläche führen kann, durch die die Transistoren beschädigt werden können. Wenn Schutzmaßnahmen fehlen, führt der Latch-up zur thermischen Zerstörung des Bauteils.

Anmerkung 3) Quelle: Renesas Electronics.

Anmerkung 4) Speicherknoten:

Flipflop-Schaltungsknoten in jeder Speicherzelle, die die einzelnen Informations-Bits als elektrisches "High"- oder "Low"-Potenzial speichern.

Anmerkung 5) Stacked Capacitors:

Stacked Capacitors sind Kondensatoren, deren beiden Elektroden aus Polysilizium oder Metall bestehen. Diese Kondensatoren werden auf der obersten Schicht der MOS-Transistoren auf dem Silizium-Substrat erzeugt, und verringern damit den Flächenbedarf der Speicherzelle.

Anmerkung 6) Thin-film-Transistor (TFT):

Ein aus Thin-film-Polysilizium erzeugter Transistor. Solche Elemente werden als SRAM-Lasttransistor genutzt und auf der obersten Schicht des CMOS-Transistors auf dem Silizium-Substrat angebracht. Mit ihnen lässt sich der Flächenbedarf der Speicherzelle reduzieren.

Anmerkung 7) komplett als CMOS realisierter Zellentyp:

Eine SRAM-Speicherzellenstruktur, die aus insgesamt sechs P-Kanal und N-Kanal MOS-Transistoren besteht, die auf der gleichen Siliziumsubstrat-Oberfläche erzeugt werden. Eine solche Speicherzelle belegt eine große Fläche und es besteht die Gefahr eines Latch-ups.

Verfügbarkeit

Die neuen SRAMs von Renesas Electronics werden im November 2013 in Muster-Stückzahlen erhältlich sein. Der Start der Serienfertigung ist für den Dezember 2013 geplant. (Änderungen bzgl. Verfügbarkeit ohne gesonderte Benachrichtigung vorbehalten.)

Hinweis:

Alle in dieser Pressemitteilung erwähnten Produkt- und Dienstleistungsbezeichnungen sind Warenzeichen oder eingetragene Warenzeichen der entsprechenden Inhaber.

Kommentare

Pressemitteilungstext: 835 Wörter, 7219 Zeichen. Artikel reklamieren

Tragen Sie jetzt Ihre kostenlose Pressemitteilung ein!

X

X